# 平成23年度「ユニバーサルリンク技術の研究開発」の研究開発目標・成果と今後の研究計画

## 1. 実施機関・研究開発期間・研究開発費

- ◆実施機関 日本電信電話株式会社(幹事者)、株式会社日立製作所、三菱電機株式会社、富士通株式会社、日本電気株式会社、エヌ・ティ・ティ・コミュニケーションズ株式会社

- ◆研究開発期間 平成20年度から平成23年度(4年間)

- ◆研究開発費 総額1294百万円(平成20年度:300百万円、平成21年度:480百万円、平成22年度:265百万円、平成23年度:249百万円)

## 2. 研究開発の目標

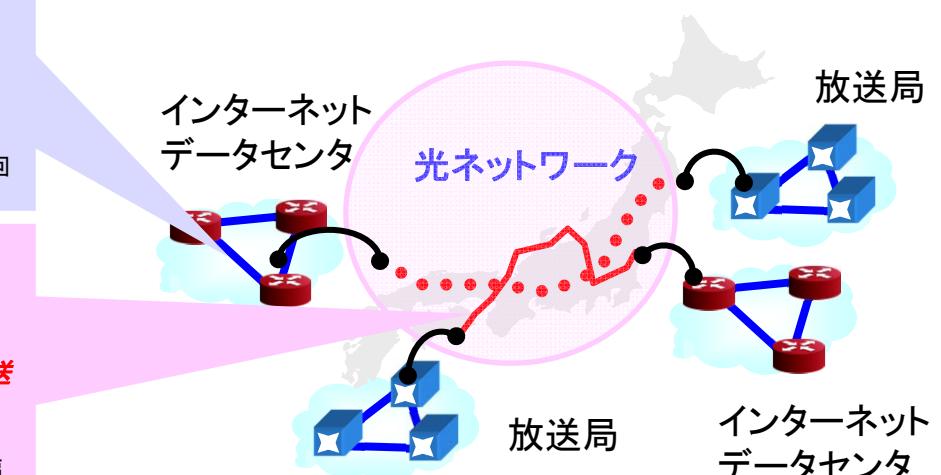

- ・複数の100ギガビット級信号(ハイビジョン映画2時間相当分を1秒で転送可能なデータ量)を、約1000km級(直線距離で東京から福岡程度)の範囲内のLAN内/LAN間で、自由に転送が可能となる電気信号基盤処理技術を2011年度までに確立する。

## 3. 研究開発の成果

本研究の概要は、以下に示す課題ア・イから構成される上記の100GbE信号転送にかかる電気信号処理技術の確立である。本分野における積極的な国際標準化貢献、基盤技術開発の先行的着手を通じ、日本の国際競争力強化を図る。

### 課題ア LAN向け100GbE対応パラレルリンク技術 (日立)

- インターネット・データセンタ内の伝送を10-100倍に高速化し、電力を1/10に低減する100ギガビットイーサネット向け回路技術

- 毎秒25ギガビットの光信号を4つ多重して1本の光ファイバに伝送 (最大40km)

- イーサネットの国際標準をリード

#### 《具体的な成果目標》

- LAN向け100GbE対応パラレルリンク技術の確立を目指し、同技術の下記回路を開発する。

- ◆ MAC・PCS間省電力・高速MLD(Multi Lane Distribution)インターフェース

- ◆ 多重分離回路や符号/復号化処理を実現するPCS回路(Physical Coding Sublayer)

- ◆ MAC回路(Media Access Control)

- 上記開発回路をMLDインターフェース対応速度変換LSIと、FPGA等の論理回路にそれぞれ集積回路化し、実用上重要な性能である信号速度、省電力性能や信号品質を実機実証する。

### 課題イ WAN向け100GbE信号トランSPORT対応デジタル信号波形歪補償処理技術

(NTT、三菱、富士通、NEC、NTTコム)

- 長距離ネットワーク内の伝送を10倍に高速化し、高信頼に伝送する100ギガビット光ネットワーク向け回路技術(0-500km相当距離を柔軟に伝送)

- 1波長あたり毎秒100ギガビットの光信号を複数多重して1本の光ファイバで大容量伝送

- 光ネットワークの国際標準をリード

#### 《具体的な成果目標》

- OTN(Optical Transport Network)において10Gbpsを超えるシリアル光信号伝送で課題となる偏波モード分散ならびに波長分散とともに超高速波形歪を、送信端及び受信端の超高速デジタル信号処理技術により、リアルタイムに波形歪補償し長距離伝送可能な基盤技術の開発を行う。

- OTU4信号フレーム相当のスループットで、以下の伝送波形歪をリアルタイムに補償し高信頼に伝送するLSIを実現するための信号処理アルゴリズムを確立し、少なくとも10Gbps以上のスループットでの動作検証を行う。

- ◆ 偏波モード分散変動: 0-50ps

- ◆ 波長分散変動: 0-20000ps/nm

## 研究開発目標

## 研究開発成果:

## 課題ア LAN向け100GbE対応パラレルリンク技術

(株式会社日立製作所)

- ア-1 MAC・PCS間省電力・高速MLDインターフェースの開発

- ア-2 論理回路機能の開発

- ア-3 送受信器機能の試作評価検証

## (1) MLD対応速度変換LSI

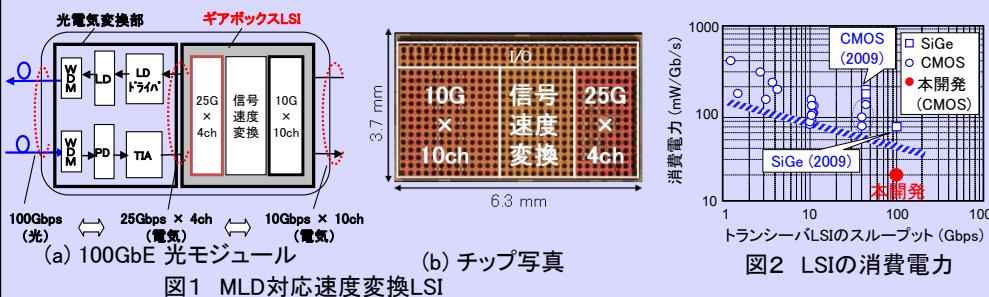

- インタフェース回路( $25\text{Gbps} \times 4\text{ch}$ ,  $10\text{Gbps} \times 10\text{ch}$ )と信号速度変換を集積した、100ギガビットイーサネット(100GbE)向けMLD対応速度変換LSIを、世界に先駆けCMOS-LSIで開発(図1)

- 回路の低電力方式の開発により、従来(SiGe-LSI)比1/4となる消費電力2Wを実現(図2)

## (2) 並列レーン縮退伝送技術

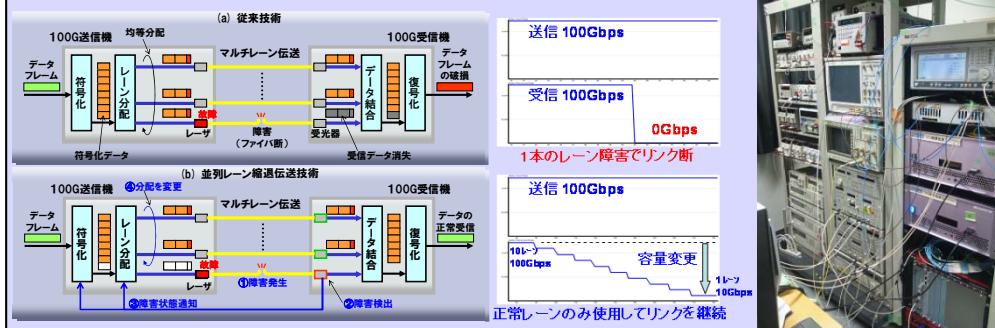

- 100GbEの並列レーン伝送において、レーン障害発生時にも縮退運転(低容量伝送)により、リンクを維持し、データ伝送を継続可能な縮退伝送技術を開発(図3)

- 100GbEから40GbE/10GbEへ相互接続可能な速度変換機能を追加し、機能検証機(図4)とMLD速度変換LSIとを接続した課題間接続実験、及びOTNを経由したフィールド伝送実験(図5)を行い、実機実証を完了。

図5 フィールド伝送実証実験

## 研究開発成果:

## 課題イ WAN向け100GbE信号トランスポート対応デジタル信号波形歪補償処理技術

- イ-1 リアルタイムデジタル信号処理アルゴリズム

- イ-2 アルゴリズム実証のための回路試作と評価検証

## イ-1-1 直交周波数多重分離信号処理アルゴリズム開発

イ-2-1 直交周波数多重分離信号処理回路試作と機能実証およびリアルタイム信号処理評価技術

(日本電信電話株式会社)

- ① 波形歪補償の回路規模低減に関し、周波数領域等化アルゴリズム優位性の明確化・方針策定

- ② ITU-T勧告 G.709、G.696.1勧告における100GE over OTNに関する標準化獲得

- ③ 世界最大容量8Tbpsフィールド実験(オフライン)における提案アルゴリズムの動作実証

- ④ OFDM技術を応用した波長分散推定アルゴリズム技術確立と40Gbpsリアルタイム動作実証

- ⑤ 入出ユーティリティ関連技術(誤り訂正符号・偏波多重QPSK変調)との連係動作確認

G.709勧告における100Gbps階梯OTU4の国際標準化の提案・勧告化成果②

波長分散推定機能を実装した40Gbpsリアルタイムデジタル信号処理回路装置の実現

成果④-⑤(課題イ-2-3, 4と連携)

**研究開発成果:課題イ WAN向け100GbE信号トランスポート対応デジタル信号波形歪補償処理技術**

**イ-1 リアルタイムデジタル信号処理アルゴリズム / イ-2 アルゴリズム実証のための回路試作と評価検証**

**イ-1-2 送信端デジタル信号処理アルゴリズム開発****イ-2-2 送信端デジタル信号処理回路試作と機能実証**

(三菱電機株式会社)

- ① 送信端デジタル信号処理による大規模波長分散補償アルゴリズムを策定

- ② 多値伝送の送信部実現のキーコンポーネントとして 40GSample/s超級 D/A 変換回路の試作・評価を実施

- ③ SiGe BiCMOSプロセスによる波長分散補償用デジタル信号処理回路試作を完了

半導体TEGによるD/A変換回路

出力波形例

デジタル信号処理試作回路

- ④ 平成22年度に試作した試作回路の単体評価を終了後、課題アとの課題間接続試験を実施。課題ア装置との連携により、100GbE信号のエラーフリー伝送を達成

- ⑤ 2011年11月にJGN-Xテストベットを使用して課題間連携実験を実施、課題間の相互接続性確認実験を完了

課題間接続試験

課題イ(三菱電機)と課題ア(日立)

(2011年10月)課題間連携実験における

送信端デジタル信号処理回路装置

(2011年11月)**イ-1-3 高安定デジタルコヒーレント検波偏波制御信号処理アルゴリズム開発****イ-2-3 高安定デジタルコヒーレント検波偏波制御信号処理回路試作と機能実証**

(富士通株式会社)

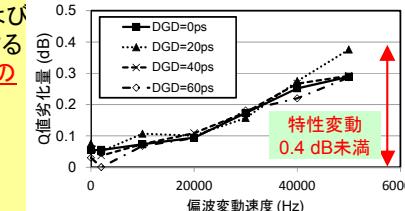

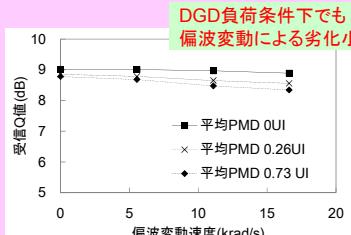

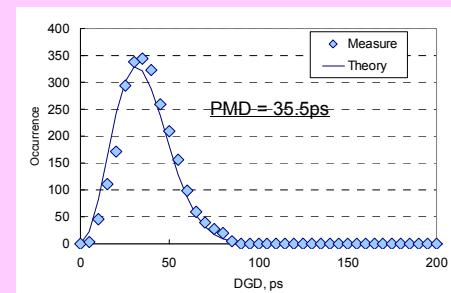

- ① 最大50ps の偏波モード分散(DGD)および20kHz 以上の高速偏波変動条件下であっても、高安定に受信することが可能な偏波制御信号処理アルゴリズムの仕様を策定

最適なアルゴリズムの選定および回路設計パラメータを明確にすることでDGD 50ps, 20kHz以上の偏波変動追従性を実現

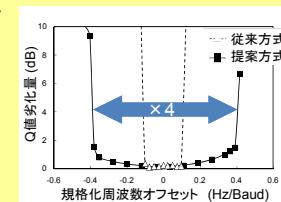

従来方式と比較して

周波数誤差推定範囲が約4倍広い

新方式を提案

ハードウェアに対する要求が緩和されるフィードフォワード型を採用、ハードウェアエミュレータによりレザ位相雑音に対する長時間安定性を確認

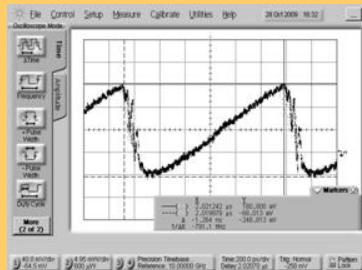

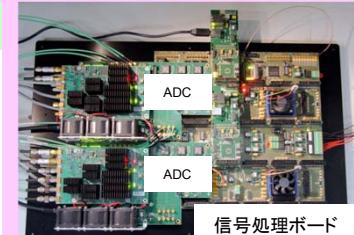

- ② 10Gbps超のスループットを有するリアルタイム動作可能なデジタル信号処理演算回路を試作、DGD条件下での高安定偏波変動追従性能を評価

信号処理ボード

- ③ 開発したアルゴリズムを搭載した40Gbpsのデジタルコヒーレント送受信器でフィールド伝送実験を実施、DGD 50psと25kHz以上の偏波変動負荷した条件で安定受信を確認

**研究開発成果:課題イ WAN向け100GbE信号トランスポート対応デジタル信号波形歪補償処理技術**

**イ-1 リアルタイムデジタル信号処理アルゴリズム / イ-2 アルゴリズム実証のための回路試作と評価検証**

**イ-1-4 受信端デジタル信号処理アルゴリズム開発****イ-2-4 受信端デジタル信号処理回路試作と機能実証**

(日本電気株式会社)

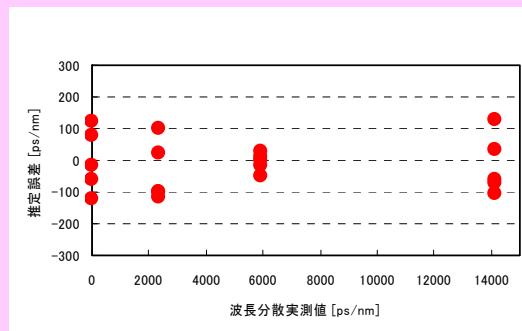

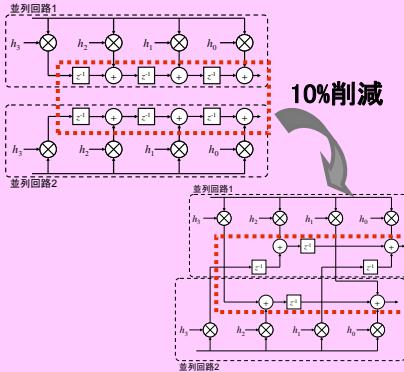

受信端の分散歪補償では、数100シンボルに及びインパルス応答長に

対応可能な巨大フィルタの回路規模制限下での実現が課題

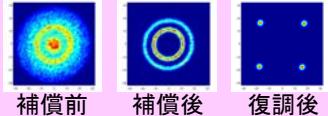

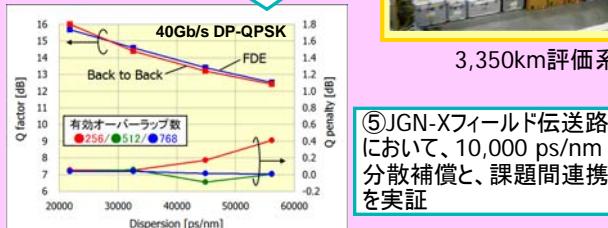

⇒成果①②(イ-1-4)と成果③～⑤(イ-2-4)により10,000ps/nm波長分散補償を達成

**時間領域等化方式**

- ①遅延器配置の最適化により回路規模を削減する並列化方式の提案

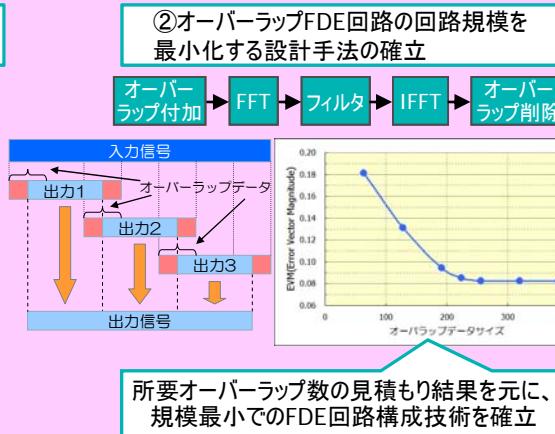

**周波数領域等化方式**

- ②オーバーラップFDE回路の回路規模を最小化する設計手法の確立

所要オーバーラップ数の見積もり結果を元に、規模最小でのFDE回路構成技術を確立

**40Gb/s級光信号の周波数領域歪補償のリアルタイム実証****FPGAベース試作回路でのリアルタイム分散補償**

③FPGAベース試作回路を用いたリアルタイム補償の基本実証に成功

**長距離伝送路でのリアルタイム無劣化補償と最適化設計実証、フィールド伝送路での課題間連携実証**

- ④約80kmxSMF40span=3350km伝送路において劣化ない分散補償と、最適回路設計手法を実証

- ⑤JGN-Xフィールド伝送路において、10,000 ps/nm分散補償と、課題間連携を実証

**イ-2-5 フィールド運用・評価技術**

(エヌ・ティ・ティ・コミュニケーションズ株式会社)

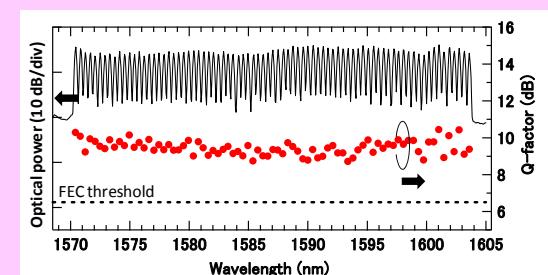

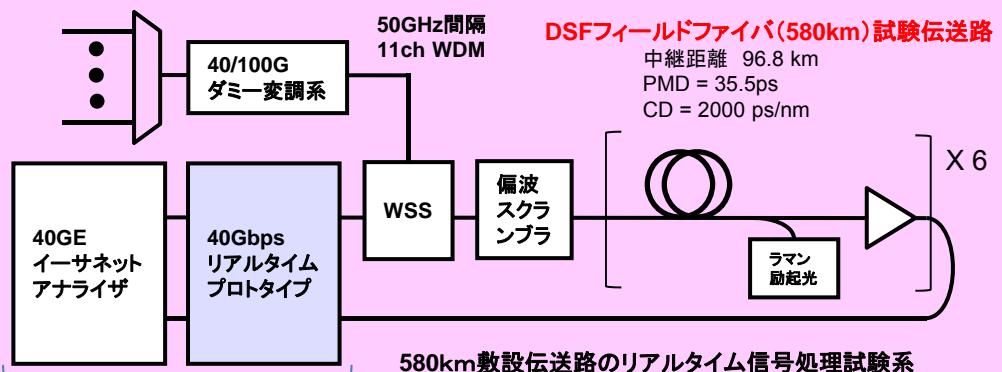

**① リアルタイム試験伝送路の構築**

- 敷設の分散シフトファイバ(Dispersion Shifted Fiber: DSF)を用いて、0～50ps以上の偏波モード分散(PMD)と、2000ps/nm以上の波長分散(CD)を有する50GHz間隔11波WDM伝送試験伝送路(580km)を構築。

- 試験伝送路の偏波モード分散特性を評価し、理論解析から導出される発生分布と一致することを確認し、試験伝送路特性モデルを評価。

**②40ギガーサignal(40GE)のリアルタイム伝送特性を確認**

- 試験伝送路を用いた40GE信号導通試験を実施。実用的な偏波変動を与えた状況下において、クライアント信号のレベルでの安定なエラーフリー伝送を実証。

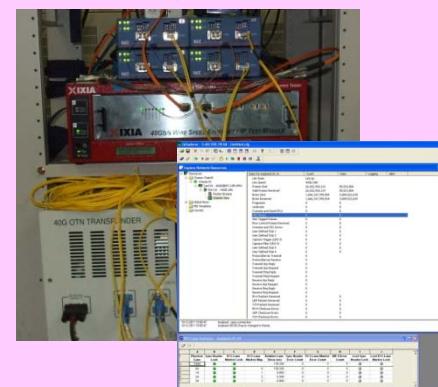

580km敷設伝送路のリアルタイム信号処理試験系

40GE信号のエラーフリー伝送

580km敷設伝送路の偏波モード分散特性

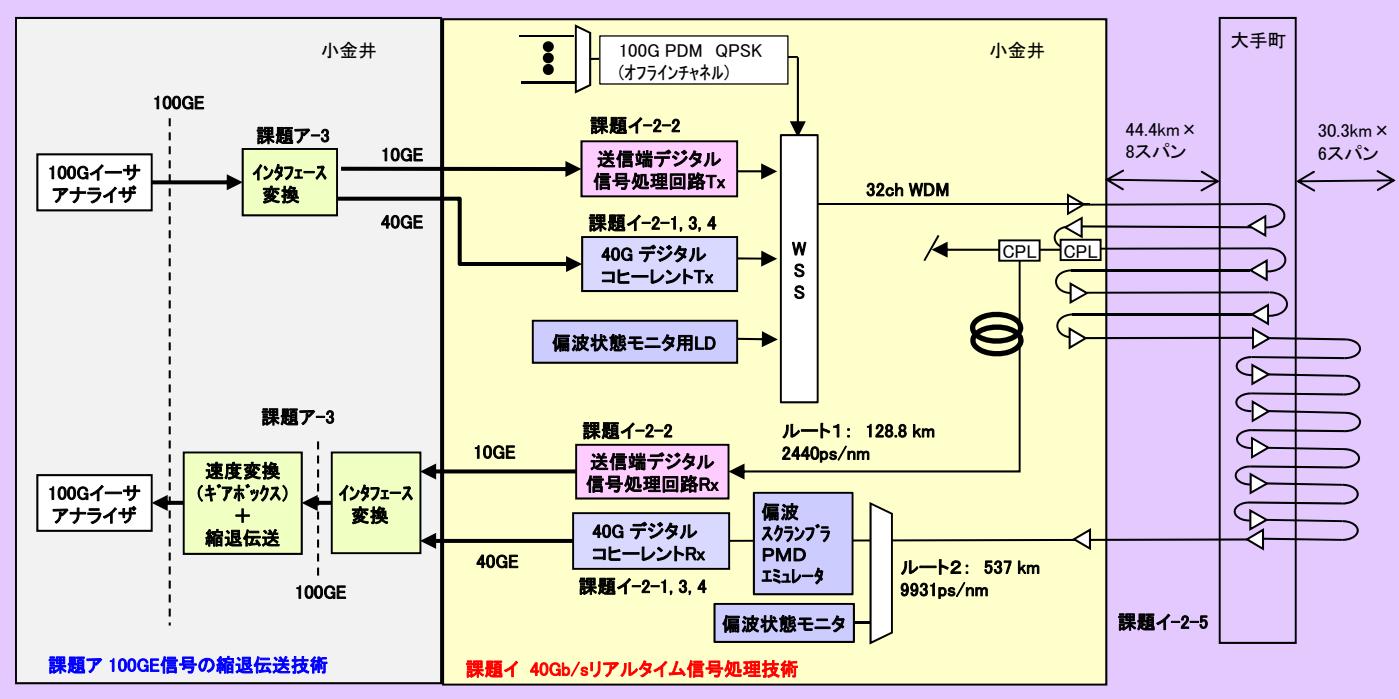

## 研究開発成果:課題ウ 540km 敷設ファイバ(JGN-X)を用いた課題間連携リアルタイムWDM伝送実験

INCT本部オープンラボに各課題の試作装置を持ち寄り、小金井・大手町間に敷設されたSMF敷設ファイバ(JGN-X)を用いて、32ch波長多重伝送実験系を構築し、100GbE信号をLANからWANまでシームレスに伝送するための以下の電気信号処理要素技術を確立し、リアルタイム動作を実証。

課題ア: LAN内又はLANからの100Gbpsイーサネット信号(100GbE)を伝送する省電力パラレルインタフェース(25Gbps × 4)用信号変換電気信号処理技術

課題イ: WANにおいて100GbE信号を光ネットワーク(OTN: Optical Transport Network)を介して長距離伝送するためのシリアルインタフェース用

デジタル信号波形歪補償技術(光ファイバSMF換算1000km以上の波長分散(0-20000ps/nm)及び、偏波モード分散0-50psをダイナミックに補償)

課題ア-3 MAC/PCS検証機(左)

課題イ-2-2 送信端デジタル信号処理回路(右)

課題イ-2-1, 3, 4 40Gデジタルコヒーレント

送受信回路と検証系

4. これまで得られた成果(特許出願や論文発表等) \* 成果数は、累計件数と( )内の当該年度件数です。

|                  | 国内出願      | 外国出願       | 研究論文       | その他研究発表     | プレスリリース  | 展示会       | 標準化提案    |

|------------------|-----------|------------|------------|-------------|----------|-----------|----------|

| ユニバーサルリンク技術の研究開発 | 46<br>(9) | 43<br>(10) | 73<br>(16) | 120<br>(26) | 9<br>(3) | 15<br>(6) | 8<br>(0) |

5. 研究成果発表会等の開催について

(1) 学会発表・表彰

- IEEE J-LT特集号 “Trends in signal processing for lightwave transmission” を企画・編集、一部成果を発表(H21)

- OECC2011(2010年7月)ポストデッドライン論文に採択。世界最大容量 8 Tbps フィールド実験に成功(H22)

- 2010年 OCS研究会論文賞受賞(2010年12月)。デジタルコヒーレント伝送システムのための逆伝播型非線形効果補償とその半ブラインド最適化(H22)

- 2011年 レーザー学会優秀論文発表賞を受賞(2011年5月)。Mach-Zehnder変調器多段接続時の自動バイアス制御に関する検討(H23)

- OECC2012(2011年7月 高雄)にて最優秀論文賞を受賞。100Gオフラインフィールド実験におけるPMD特性評価結果を発表(H23)

(2) 展示会

- 第10回 光通信技術展FOE: 100GbE over OTNに関する国際標準化貢献についてパネル展示。(H21)

- 第24, 25回 光通信システム(OCS)シンポジウム(2010/2011年12月 静岡県三島市)でパネル展示、プロトタイプ出展(H22/23)

- ICC2011 (2011年6月 京都京都府、国立京都国際会館) でパネル展示

(3) 報道発表

- フォトニック3PJ連携実験(2009年12月): 関係PJとして、ITU-T SG15委員会において、提案100GbE over OTN方式に関する国際標準化に成功(H21)

- 「100ギガビットイーサネット向け超低消費電力トランシーバ回路を開発」(2010年2月): 1Gb/sあたりの消費電力が1mW以下のトランシーバ回路の開発(H21)

- フォトニック3PJ連携実験(2010年12月): 関係PJとして、100GbE over OTNに関する要素技術の実証実験に成功(H22)

- 「世界初、100Gbps 及び40Gbps 光通信のプラグアンドプレイを超高速で実現」(2011年11月): デジタルコヒーレント光伝送による超高速自動設定技術を敷設ファイバ環境下で実証(H23)

6. 今後の研究開発計画

課題ア: 本PJにて開発したパラレルリンクに関する要素技術は、現行の100Gbps Ethernetのみならず、次世代の高速Ethernetや、装置内の超近距離光伝送(光バックプレーン等)にも応用できる技術である。今後、本技術を発展し、次世代高速化技術や応用技術の研究開発を推進する。

課題イ: 本PJ開発要素技術を他の周辺要素技術を融合し、100Gbps級リアルタイムデジタル信号処理(DSP)を用いたシステム統合技術を確立するとともに、DSP技術のさらなる発展(超高速化ならびに適用変調等高機能化)により、光ネットワークのより柔軟な運用を可能とする研究開発を推進する。

課題ウ: プロジェクト内の課題ア、イの課題間連携およびユーティリティ技術との連携についてはJGN-Xテストベッドを用いた540kmフィールド実験に成功し、本結果を今後の研究開発の推進に役立てる。