## 平成23年度研究開発成果概要書 「究極立体映像用超高密度・超多画素表示デバイスの研究開発」

#### (1) 研究開発の目的

特殊なメガネを装着しないで自然な裸眼立体映像を提示する技術の研究開発 が種々進められている。その中で、ホログラフィ方式は光の波面そのものを再 現することが可能であることから、理想的な立体映像表示が実現できる。この ホログラフィの原理、優れた特長を電子映像システムで実現する電子ホログラ フィは、究極の立体映像提示システムとして、各種動画メディア、コミュニケ ーションメディア分野への応用が期待されている。しかしながら、電子ホログ ラフィでは、光の回折作用によって立体像を提示することから、十分な視域角 と画質を得るためには、表示デバイスである空間光変調素子の画素を極めて高 密度で構成する必要がある。さらに、表示立体像の大きさが空間光変調素子サ イズの制限を受けることから、画素ピッチを高密度化するのみでなく、表示画 素数についても膨大な画素数を必要とする。この要求に対して、現在実現可能 な空間光変調素子の画素密度・画素数はいずれも大幅に不足しており、今後、 電子ホログラフィ技術を用いた実用的なシステムの可能性を切り開くためには、 空間光変調素子の高画素密度化、高画素数化に関する技術をいかに進展させる が大きな課題である。日本の高度なデバイス技術、電子映像技術を活かして、 この課題のブレイクスルーをいち早く実現し、同じく立体映像技術の開発に積 極的に取り組んでいる米、欧、アジア各国に技術先行することは今後、本分野 で国際競争力を発揮していく上でも極めて重要である。

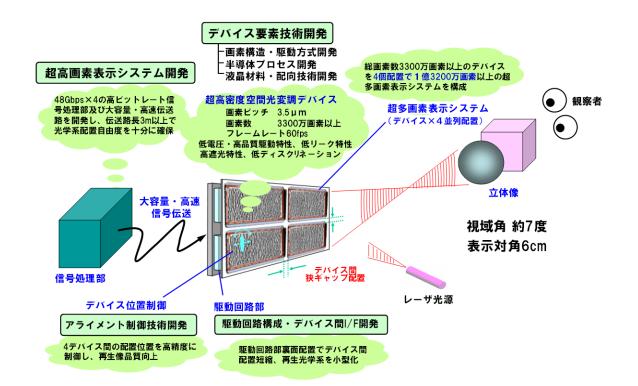

本研究開発課題は、次世代の電子ホログラフィ研究で広く利用可能な超高密度、超多画素空間光変調素子を実現するためのデバイスおよびその製造に関する研究開発を通じて目標仕様を達成するとともに、今回の試験研究以降のさらなる高密度化・超画素化要求に応えるための基礎となり得る技術の蓄積を図ることを目的とする。具体的には、最終年度(平成25年度末)に画素ピッチ4um未満、総画素数1億2000万画素以上(デバイス4並列配置)の超高密度・超多画素空間光変調デバイスを実現し、電子ホログラフィ研究に利用可能な世界最高レベルの表示デバイスを提供することを目標とする。

# (2)研究開発期間平成23年度から平成25年度(3年間)

### (3) 委託先企業 株式会社 J V C ケンウッド < 単独 >

#### (4) 研究開発予算(百万円)

平成 23 年度240 (契約金額)平成 24 年度226 ( " )平成 25 年度212 ( " )

#### (5) 研究開発課題と担当

課題ア:究極立体映像用超高密度・超多画素表示デバイスの研究開発

- 超高密度 LCOS バックプレーン技術の開発 ((株)JVC ケンウッド)

- 2. 超高密度画素対応 液晶技術の開発 ((株)JVC ケンウッド)

- 3. デバイス並列配置による超高画素表示システムの開発 ((株)JVC ケンウッド)

#### (6) これまで得られた研究開発成果

|      |         | (累計) 件 | (当該年度)件 |

|------|---------|--------|---------|

| 特許出願 | 国内出願    | 0      | 0       |

|      | 外国出願    | 0      | 0       |

| 外部発表 | 研究論文    | 0      | 0       |

|      | その他研究発表 | 0      | 0       |

|      | プレスリリース | 0      | 0       |

|      | 展示会     | 0      | 0       |

|      | 標準化提案   | 0      | 0       |

#### 具体的な成果

(1) 反射型液晶表示デバイス(LCOS)の画素高密度化の課題である画素トランジスタ素子の必要耐圧低減に対応するため、新たな画素回路方式を提案し、画素ピッチ 3.5 μm の画素回路の開発とレイアウト設計を実施した。また、画素構造および半導体プロセス開発として、a)画素トランジスタ形成部の多重ウェルでフォトキャリアを吸収する高耐光性構造 b)画素信号電圧特性の向上を実現するための複数層スタック MIM (Metal-Insulator-Metal) 容量構造の適用など、画素駆動特性向上のための新構造、新プロセスを開発した。また、画素トランジスタのリーク電流について専用 TEG による測定を行い、常温 25℃でサブ fA オーダの低リーク特性実現の見通しを得た。以上の画素設計と画素構造およびプロセス開発を適用し、方式検証用テストデバイスは、「つなぎ露光プロセス」が不

要な画素数範囲、かつ実駆動での表示デバイス特性の評価検証と課題抽出が十分に可能な規模が必要である点を勘案し、画素数規模を 最終目標デバイスの 1/4 (885 万画素) とした。

- (2) 超多画素表示デバイスの課題である駆動信号の大容量・高レート化に対応するため、① D/A 変換内蔵型ドライバ ②高速デジタルデータ I/F の仕様開発、回路設計およびレイアウト設計を実施し、前出の方式検証用テストデバイスの周辺ドライバ構成に適用した。内蔵D/A 変換回路にはカラムデータ比較方式を採用し、最大 300 (MHz) レートの階調基準カウンタとカラムデータ比較動作によって全カラムデータを同時並列的に D/A 変換する。検証用テストデバイスには、10bit 階調のデジタルデータに対して最大 1. 2GSPS の高レート D/A 変換に対応した設計を適用した。また、表示デバイスへの高速デジタルデータ I/F 方式については、汎用 FPGA の直接接続が可能で高速データ転送が可能な DDR2 (SSTL18) を採用した。これにより方式検証用テストデバイスにおいて、実質 12Gbps の高レートデータ入力 I/Fを実現した。

- (3) 反射型液晶表示デバイスでは、液晶の電圧-変調度特性の要求から、 半導体基板の画素回路を高動作電圧に対応させる必要あり、トランジ スタサイズが大きくなる結果、画素微細化が制約される課題がある。 また、高密度画素に対して良好な空間変調応答特性を実現するため、 液晶層ギャップ、配向条件開発が必要となる。本年度は、要素開発と して、①低駆動電圧対応の液晶材料の検討と候補選択、②液晶ギャッ プ条件と空間変調応答特性の関係について解析および評価を実施し た。検討の結果、目標画素ピッチ 4μm 未満で良好な空間変調特性を 確保するためのギャップ条件範囲の指針を得た。また、画素回路の駆 動特性で実現可能な駆動電圧範囲に対して 100%飽和点近傍までの変 調度を確保するため、低駆動電圧の液晶材料候補の選択、および電圧 -変調度特性のシミュレーション、評価を行い、駆動基板の画素回路 による実駆動条件で十分な変調特性が実現できる見通しを得た。

- (4) 最終年度の目標である複数デバイス並列配置による超多画素表示デバイス(総画素数1億2000万画素以上)の要素技術として、複数配置デバイス間の位置、チルト角、回転角を高精度に制御可能なアライメント調整機構がある。本年度は開発するアライメント機構の精度、

および制御値に対する機構レスポンスの分解能の定量評価を可能とするため、アライメント精度測定治具を製作した。本測定治具は被測定デバイス面にレーザー光源を入射し、反射1次回折光のビーム位置からチルト角を秒オーダで検出する機能、顕微鏡カメラでデバイス面の基準パターン座標を基準点としてxyz変位、回転角を測定する機能を複合した高精度の6軸測定が可能であり、次年度以降のアライメント機構開発における機構精度の測定、複数配置表示デバイスのアライメント調整確認に活用していく。また、本年度は上記(2)のD/A内蔵型ドライバ方式を適用した検証用テストデバイスの駆動回路、信号処理回路の回路設計、基板開発を行い、検証用テストデバイスの表示動作確認、駆動特性の評価環境を構築した。テストデバイスに適用したドライバ構成は最終デバイスのベース構成となるため、本年度に実施した回路開発の設計リソースは、最終デバイスの駆動回路開発にも活用が可能である。

#### (7)研究開発イメージ図