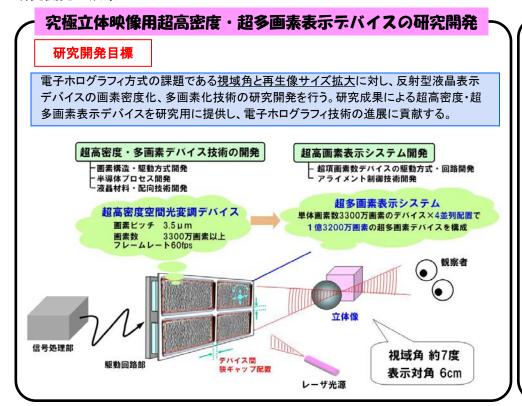

# 平成24年度「究極立体映像用超高密度・超多画素表示デバイスの研究開発」の 研究開発目標・成果と今後の研究計画

## 1. 実施機関・研究開発期間・研究開発費

◆実施機関 株式会社JVCケンウッド(単独)

◆研究開発期間 平成23年度から平成25年度(3年間)

◆研究開発費 総額678百万円(平成24年度 226百万円)

#### 2. 研究開発の目標

電子ホログラフィ方式は、光の波面そのものを再現でき、自然な奥行き知覚が可能な究極の立体提示方式であるが、実用的な視域角と再生像サイズの実現には、空間光変調デバイスの画素密度、画素数が大幅に不足しており、超高密度・超多画素表示デバイスの実現が課題である。本研究開発は、反射型液晶表示デバイス技術をベースに、超高密度画素と超多画素を実現する上での課題を解決するための研究開発を行い、将来の電子ホログラフィ研究用に広く利用可能な世界最高レベルの表示デバイスを実現することを目標とする。最終年度(平成25年度)には、画素ピッチ4um未満、総画素数1億2千万画素以上の超高密度、超多画素表示デバイスを製作し、電子ホログラフィ研究用に提供する。

### 3. 研究開発の成果

### 【H24年度実施内容と成果概要】

- 1. 超高密度画素LCOSバックプレーン方式開発

- ①目標画素ピッチ3.5 µm(4 µm未満)に対応した新画素回路、画素構造の検証

- ②D/A変換内蔵型ドライバ、高速データ入力対応データI/F回路方式の検証。

- ⇒①②の新回路方式、および設計検証を目的とした先行テストデバイスの素子化・詳細 評価を実施し、実駆動での表示動作を確認。バックプレーン方式の有効性を実証した。

- 2. 超高密度画素対応液晶技術開発

- ①低駆動電圧(高 Δ n)液晶材料候補の評価・絞り込みを行い最終デバイス用材料を選定。 ②動画特性の見地から液晶応答時間のギャップ、温度依存性の検討と評価を実施。

- 3. 超多画素表示システムの要素開発

- ①最終仕様デバイス(3300万画素)駆動回路、映像入力I/F回路の設計と基板開発を実施

- ②複数デバイス配置のアライメント機構用の仕様作成、構造検証と試作評価を実施。

## 究極立体映像用超高密度・超多画素表示デバイスの研究開発 平成24年度の主な成果

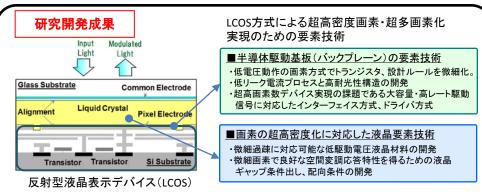

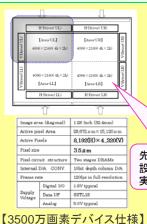

## 課題ア-1 超高密度・多画素LCOSバックプレーンの開発 ①

画素ピッチ3.5µmの超高密度、超多画素LCOSデバイスのベースとなる画素回路 方式、内蔵ドライバ方式の先行テストデバイスによる検証を実施し、最終デバイス バックプレーン実現に向けた要素技術と基本設計を確立した。

※画素数:885万画素(4K2K)

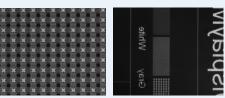

世界最高レベルの超高密度画素 LCOS素子で実画像表示を確認

3.5µm画素ピッチ テストデバイスの実表示画像

- ①先行開発のテストデバイス用バックプレーン(885万画素:4K2K画素数)に液晶工程 を適用し表示デバイスを構成、実駆動条件での画像表示動作を確認した。

- ②テストデバイスによる画素回路、内蔵ドライバの方式検証、および各構成要素の基 本設計、特性評価を実施し、最終目標デバイスの設計・開発にフィードバック。

## 課題ア-1 超高密度・多画素LCOSバックプレーンの開発 ②

先行テストデバイスによる画素構造と画素回路特性、およびデバイス内蔵ドライバ カラム比較型D/A変換部の実動作条件での評価を行い、最終デバイスへの適用が 可能な基本特性が得られていることを確認した。

#### ①3.5um超高密度画素の構造·基本特性を確立

開口率85% 反射率62%

~実用レベルの 画素横造を確立

#### 電圧保持期間での傾斜なし

低リークトランジスタ 光キャリア吸収構造

~良好な電圧保持特性 を実現

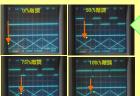

#### ②カラム比較型D/A変換の動作・設計を確立

映像データレート300MHz D/A変換基準クロック300MHz

~実駆動条件での安定動作を 確認し、最終デバイスへの 適用に目途。

## 課題ア-1 超高密度・多画素LCOSバックプレーンの開発 ③

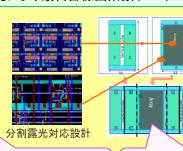

最終目標画素数デバイス(単体画素数=3500万画素)のLCOS方式バックプレーン の仕様開発、回路設計、半導体マスク開発を実施し、1stウェハサンプルを製作。 分割露光対応設計とプロセス開発により最終目標画素数デバイスサイズに対応。

先行4Kテストデバイスのレイアウト 設計のミラー配置構成で、先行で 実施した設計検証の実績を反映

画素配列エリアについては分割 なし、一括露光する仕様を採用、 歩留、表示特性への影響を低減

最終デバイス用バックプレーンのマスク設計 開発に反映、初回ウェハーサンプルを製作

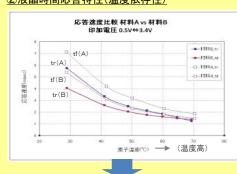

## 課題ア-2 超高密度画素対応 液晶技術の開発

最終仕様デバイス液晶材料候補、セルギャップ条件を検討。液晶材料の候補を 2種に絞込み、各材料について配向、ギャップ形成条件出しを行った。電圧-変調 度特性、時間応答特性を評価し、各々の特性を明らかにした

#### ①液晶材料検討と候補絞込み

#### ②液晶時間応答特性(温度依存性)

電子ホログラフィ動画表示特性、面順次カラー化 対応を想定し液晶の時間応答特性の評価を実施。 (材料、ギャップ、温度条件依存)

## 究極立体映像用超高密度・超多画素表示デバイスの研究開発 平成24年度の主な成果

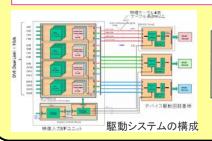

## 課題ア-3 デバイス並列配置による超多画素表示システム開発

最終年度目標の4面並列配置 表示デバイスのアライメント調整機構の構想設計、 と課題抽出、試作確認を実施。また、3500万画素表示デバイスの駆動回路、映像 入力I/Fの設計と基板開発を行い、最終デバイスの実駆動評価環境を構築した。

#### 最終画素数デバイス駆動回路システム開発

・3500万画素表示デバイスの駆動回路 システムの仕様設計、回路設計、基板 開発を行い、最終デバイス駆動と映像 信号入力による動作確認環境を構築。

#### 4面並列デバイスのアライメント機構開発

- ・機構構想と仕様案を作成し、CADによる構造確認、課題抽出を実施。

- ・近接配置によるスペース制約を軽減 する調整操作部を遠隔配置可能な 調整機構を導入、試作検証を実施。

配置・機構構造のCAD確認

4. これまで得られた成果(特許出願や論文発表等) ※成果数は累計件数と()内の当該年度件数です。

|                                     | 国内出願     | 外国出願  | 研究論文     | その他研究発表 | プレスリリース | 展示会      | 標準化提案 |

|-------------------------------------|----------|-------|----------|---------|---------|----------|-------|

| 究極立体映像用超高<br>密度・超多画素表示<br>デバイスの研究開発 | 2<br>(2) | 0 (0) | 0<br>(0) | 0 (0)   | 0 (0)   | 0<br>(0) | 0 (0) |

- 5. 研究成果発表会等の開催について

- (1)産学官連携のための運営会議の主催

NICT自主研究テーマとの連携を図るため、進捗報告会を2回(第1回:2012/05/30、第2回:2013/01/29)開催、自主研究テーマ担当者への進捗報告と 情報交換を行った。

(2)国際会議の開催

| 特になし。 |

|-------|

|-------|

- 6. 今後の研究開発計画

- (1)画素ピッチ3.5µm、デバイス単体画素数3500万画素を有する最終目標仕様デバイスの詳細評価と課題抽出、特性改善を行い、電子ホログラフィ用表示デバイスとしての最終性能を確立する。

- (2)単体3500万画素デバイス×4面並列配置により、画素ピッチ3.5µm、総画素数1億2000万画素以上の超高密度・超多画素表示デバイスと駆動回路 システムを構成し、電子ホログラフィ表示用空間光変調器として目標仕様と性能、機能を実現し、研究用途での提供を可能とする。

- (3)委託研究の最終まとめを実施するとともに、今後のさらなる画素高密度化、多画素化の実現可能性と解決すべき技術課題について考察する。